#### **General Notice**

When using this document, keep the following in mind:

- 1. This document is confidential. By accepting this document you acknowledge that you are bound by the terms set forth in the non-disclosure and confidentiality agreement signed separately and /in the possession of SEGA. If you have not signed such a non-disclosure agreement, please contact SEGA immediately and return this document to SEGA.

- 2. This document may include technical inaccuracies or typographical errors. Changes are periodically made to the information herein; these changes will be incorporated in new versions of the document. SEGA may make improvements and/or changes in the product(s) and/or the program(s) described in this document at any time.

- 3. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without SEGA'S written permission. Request for copies of this document and for technical information about SEGA products must be made to your authorized SEGA Technical Services representative.

- 4. No license is granted by implication or otherwise under any patents, copyrights, trademarks, or other intellectual property rights of SEGA Enterprises, Ltd., SEGA of America, Inc., or any third party.

- 5. Software, circuitry, and other examples described herein are meant merely to indicate the characteristics and performance of SEGA's products. SEGA assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples describe herein.

- 6. It is possible that this document may contain reference to, or information about, SEGA products (development hardware/software) or services that are not provided in countries other than Japan. Such references/information must not be construed to mean that SEGA intends to provide such SEGA products or services in countries other than Japan. Any reference of a SEGA licensed product/program in this document is not intended to state or simply that you can use only SEGA's licensed products/programs. Any functionally equivalent hardware/software can be used instead.

- 7. SEGA will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's equipment, or programs according to this document.

NOTE: A reader's comment/correction form is provided with this document. Please address comments to : SEGA of America, Inc., Developer Technical Support (att. Evelyn Merritt) 150 Shoreline Drive, Redwood City, CA 94065 SEGA may use or distribute whatever information you supply in any way it believes appropriate without incurring any obligation to you.

SEGA OF AMERICA, INC. Consumer Products Division

# SCU User's Manual

## **Third version**

Doc. # ST-97-R5-072694

© 1994 SEGA. All Rights Reserved.

## **READER CORRECTION/COMMENT SHEET**

#### Keep us updated!

If you should come across any incorrect or outdated information while reading through the attached document, or come up with any questions or comments, please let us know so that we can make the required changes in subsequent revisions. Simply fill out all information below and return this form to the Developer Technical Support Manager at the address below. Please make more copies of this form if more space is needed. Thank you.

| General                         | Informa  | tion:                                                           |            |                                                                                                                         |

|---------------------------------|----------|-----------------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------|

| Your Na                         | me       |                                                                 |            | Phone                                                                                                                   |

| Documer                         | nt numbe | r <u>ST-97-R5-072694</u>                                        |            | Date                                                                                                                    |

| Document name SCU User's Manual |          |                                                                 |            |                                                                                                                         |

| Correcti                        | ons:     |                                                                 |            |                                                                                                                         |

| Chpt.                           | pg. #    | Correction                                                      |            |                                                                                                                         |

|                                 |          |                                                                 |            |                                                                                                                         |

|                                 |          | 4                                                               |            |                                                                                                                         |

|                                 |          |                                                                 |            |                                                                                                                         |

|                                 |          |                                                                 |            |                                                                                                                         |

|                                 |          |                                                                 |            |                                                                                                                         |

|                                 |          |                                                                 |            |                                                                                                                         |

|                                 |          |                                                                 |            |                                                                                                                         |

|                                 |          |                                                                 |            |                                                                                                                         |

|                                 | I        |                                                                 |            |                                                                                                                         |

| Question                        | ns/comm  | ents:                                                           |            |                                                                                                                         |

|                                 |          |                                                                 |            |                                                                                                                         |

|                                 |          |                                                                 |            |                                                                                                                         |

| 4                               |          |                                                                 |            |                                                                                                                         |

|                                 |          | Where to send                                                   | your corre | ections:                                                                                                                |

|                                 | Fax:     | (415) 802-3963<br>Attn: Manager,<br>Developer Technical Support | Mail:      | SEGA OF AMERICA<br>Attn: Manager,<br>Developer Technical Support<br>275 Shoreline Dr. Ste 500<br>Redwood City, CA 94065 |

## **REFERENCES**

In translating/creating this document, certain technical words and/or phrases were interpreted with the assistance of the technical literature listed below.

- 1. *KenKyusha New Japanese-English Dictionary* 1974 Edition

- 2. *Nelson's Japanese-English Character Dictionary* 2nd revised version

- 3. Microsoft Computer Dictionary

- 4. *Japanese-English Computer Terms Dictionary* Nichigai Associates 4th version

## Version History

| Version 1: | April 7, 1994<br>• New draft                                       | + |

|------------|--------------------------------------------------------------------|---|

| Version 2: | May 31, 1994<br>• Revisions according to April 28, 1994 meeting    | X |

| Version 3: | July 15, 1994<br>• Revisions requested on June 30 and July 11, 199 | 4 |

## Introduction

This manual explains functions of the system controller and how they are used. The system controller transfers data rapidly and smoothly by means of the bus controls.

#### **Explanation of Terms**

The following terms are used in this manual.

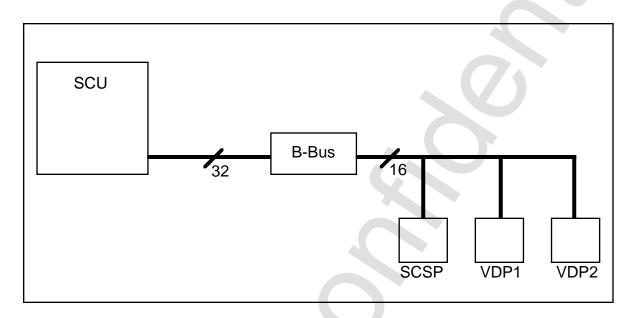

- **SCU** System Control Unit. The SCU contains the CPU I/F, A-Bus IF, B-BUS I/F, and smoothly effects data transfers between several processors connected through their respective I/F and bus. It also internally houses the DMA controller, interrupt controller, and DSP, and makes possible rapid DMA control, interrupt control, and processing of operations.

- **Main CPU** Uses a RISC type CPU SH2 that controls the overall system. SH2 contains 32-bit internal and external buses.

- **VDP1** Video Display Processor 1. Functions include character and line painting, color indication, Gouraud Shading color operations, screen output coordinate indication, and frame buffer display control.

- VDP2 Video Display Processor 2. Functions include scrolling the screen up/down/ left/right, rotating the screen, determining priority order of multiple screens, and a priority function that controls the image process of color operations and color offset.

- **SCSP** Acronym for Saturn Custom Sound Processor. This is a sound source LSI for multi-functional games that combines a PCM sound source and sound used for the DSP.

- **SMPC** System Manager and Peripheral Control. Has the functions of managing system resets, control of interfacing with output devices (control pads, mouse, etc.), time display by a real time clock, and battery backup.

- DataA bit is the smallest unit for expressing 1 or 0. 8 bits is a byte. 16 bits (or 2 bytes)<br/>is a word. 32 bits (or 4 bytes) is a 9 long word.

- **A\_Bus** Bus that connects external devices such as a ROM cassette or CD.

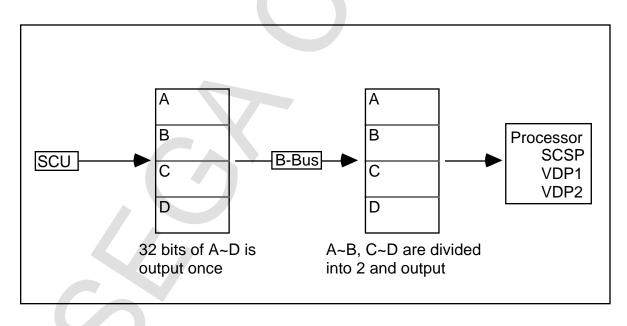

- **B\_Bus** Bus that connects VDP1, VDP2, and SCSP.

## **Manual Notations**

This manual contains the following notations.

| Binary        | Represented by " $B$ " at the end as in 100 $B$ . However, " $B$ " may be omitted for 1 bit.                                                                                                                                               |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hexadecimal   | Represented by н at the end as in 00н and FFн.                                                                                                                                                                                             |

| Unit          | 1 KByte is 1,024 bytes. 1 Mbit is 1,048,576 bits.                                                                                                                                                                                          |

| MSB, LSB      | The configuration of byte and word shows at the left the high order bit (MSB, most significant bit), and atthe right the low order bit (LSB, least significant bit).                                                                       |

| Undefined Bit | A bit not defined by an instruction word is represented by "—"                                                                                                                                                                             |

| (R)           | Represents read only data.                                                                                                                                                                                                                 |

| (W)           | Represents write only data.                                                                                                                                                                                                                |

| (R/W)         | Represents data that can be read and written.                                                                                                                                                                                              |

| ++            | Shows increments. For example, when the CT0 register is incremented, it is shown as CT0++.                                                                                                                                                 |

| x=2-0         | This indicates that 3 types exist, 2,1, and 0. For example, DxR26-0[x=2-0] in the read address in section 3.2 "DMA Control Register" means that D2R26-0, D1R26-0, and D0R26-0 exist. Similarly, D2R26-0 indicates that D2R26 ~ D2R0 exist. |

## CONTENTS

| INTRO   | DUCTION                                 |

|---------|-----------------------------------------|

| Exp     | lanation of Terms                       |

| Mar     | nual Notations                          |

|         |                                         |

|         | Figures (vii)                           |

| List of | Tables (x)                              |

| CHAPT   | TER 1 OVERVIEW                          |

|         | SCU Overview                            |

|         | System Diagram2                         |

|         | Block Diagram3                          |

| 1.2     | SCU Mapping4                            |

|         | Operation of Cache Hit5                 |

| 1.3     | SCU Register Map7                       |

|         | Level 2-0DMA Set Register 8             |

|         | DMA Forced-Stop Register 8              |

|         | DMA Status Register9                    |

|         | DSP Program Control Port 9              |

|         | DSP Program RAM Data Port 10            |

|         | DSP Data RAM Address Port 10            |

|         | DSP Data RAM Data Port10                |

|         | Timer 0 Compare Register11              |

|         | Timer 1 Set Data Register 11            |

|         | Timer 1 Mode Register 11                |

|         | Interrupt Mask Register12               |

|         | Interrupt Status Register12             |

|         | A-Bus Interrupt Acknowledge Register 12 |

|         | A-Bus Set Register                      |

|         | A-Bus Refresh Register13                |

|         | SCU SDRAM Select Register 14            |

|         | SCU Version Register                    |

|         |                                         |

| СНАРТ | ER 2 OPERATION                                            |

|-------|-----------------------------------------------------------|

| -     | DMA Transfer                                              |

|       | Basic Operation of DMA16                                  |

|       | DMA Mode                                                  |

|       | Example of a Specific Use                                 |

| 2.2   | nterrupt Control                                          |

|       | Blanking Interrupt                                        |

|       | Timer Interrupt                                           |

|       | DSP-End Interrupt                                         |

|       | Sound-Request Interrupt                                   |

|       | SMPC Interrupt                                            |

|       | PAD Interrupt                                             |

|       | DMA End Interrupt                                         |

|       | DMA-Illegal Interrupt                                     |

|       | Sprite Draw End Interrupt                                 |

| 2.3   | DSP                                                       |

|       | DSP Control from the Main CPU                             |

|       |                                                           |

|       | ER 3 REGISTERS                                            |

|       |                                                           |

|       | Register List   40                                        |

| 3.2   | DMA Control Registers 41                                  |

|       | Level 2-0 DMA Set Register 41                             |

|       | DMA Mode, Address Update, Start Factor Select Register 46 |

|       | DMA Force-Stop Register47                                 |

|       | DMA Status Register47                                     |

| 3.3   | DSP Control Ports 51                                      |

|       | DSP Program Control Port 51                               |

|       | DSP Program RAM Data Port 53                              |

|       | DSP Data RAM Address Port 53                              |

|       | DSP Data RAM Data Port54                                  |

| 3.4   | Timer Registers                                           |

|       | Timer 0 Compare Register 55                               |

|       | Timer 1 Set Data Register55                               |

|       | Timer 1 Mode Register                                     |

| 3.5 Interruj | ot Control Registers           | 57    |

|--------------|--------------------------------|-------|

| Interru      | pt Mask Register               | 57    |

| Interru      | pt Status Register             | 58    |

| 3.6 A-Bus    | Control Registers              | 61    |

|              | Interrupt Acknowledge Register |       |

| A-Bus        | Set Register                   | 62    |

| A-Bus        | Refresh Register               | 72    |

| 3.7 SCU Co   | ontrol Registers               | 73    |

|              | DRAM Select Register           |       |

| SCU V        | ersion Register                | 73    |

| CHAPTER 4 D  | OSP CONTROL                    | 75    |

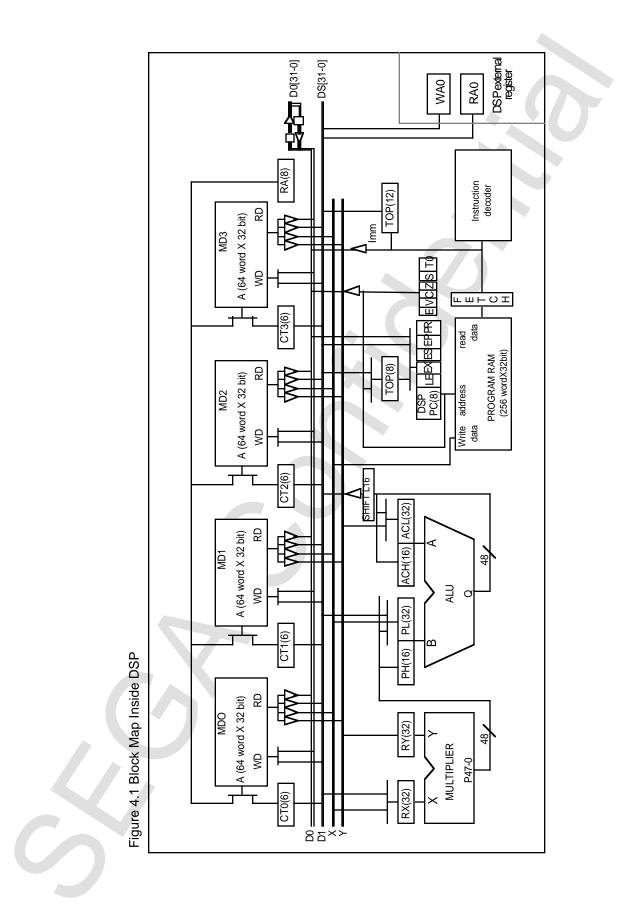

| 4.1 DSP Int  | ernal BLOCK MAP                | 76    |

|              | Commands                       |       |

| 4.3 Operan   | d Execution Methods            | 85    |

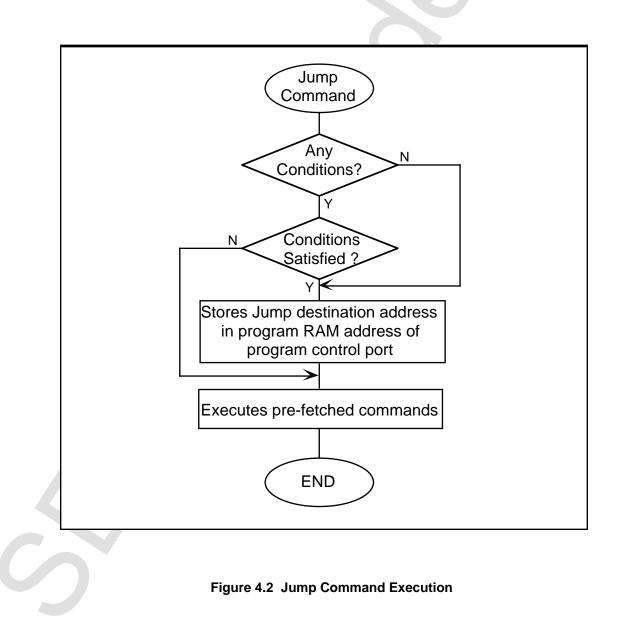

| Jump         | Command Execution              | 85    |

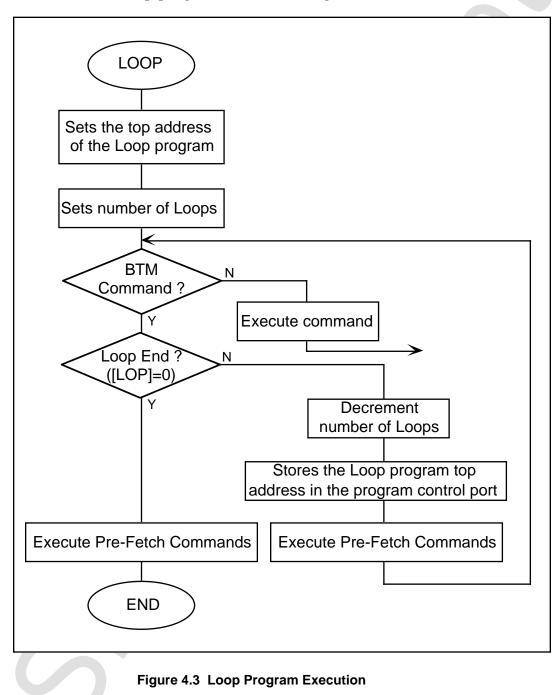

| Loop (       | Command Execution              | 86    |

| DMA (        | Command Execution              | 87    |

| End C        | ommand Execution               | 88    |

| 4.4 Special  | Process Execution              | 89    |

| Loadir       | g a Program by the DMA Command | 89    |

| Repea        | ting One Command               | 89    |

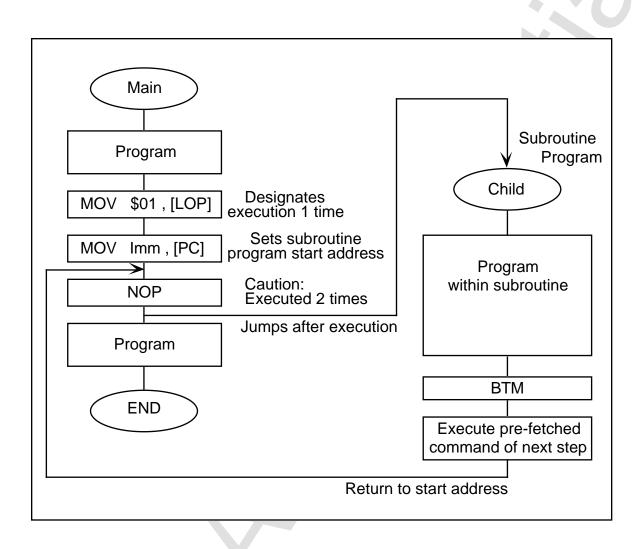

| Execu        | ting a Subroutine Program      | 90    |

| 4.5 More A   | bout Commands                  | 91    |

| Opera        | tion Commands                  | 91    |

| Load I       | mmediate Command               | . 120 |

| DMA (        | Command                        | . 132 |

| Jump         | Commands                       | . 141 |

| Loop E       | Bottom Commands                | . 153 |

| END C        | Command                        | . 156 |

|              |                                |       |

|              |                                |       |

|              |                                |       |

|              |                                |       |

|              |                                |       |

|              |                                |       |

|              |                                |       |

## List of Figures

| List of Figures                                 |  |

|-------------------------------------------------|--|

| (Chapter 1 Overview)                            |  |

| Figure 1.1 Diagram of System2                   |  |

| Figure 1.2 Block Diagram                        |  |

| Figure 1.3 SCU Mapping (Cache_address) 4        |  |

| Figure 1.4 Explanation of Cache Hit Operation   |  |

| Figure 1.5 SCU Mapping (Cache_through_address)6 |  |

| Figure 1.6 SCU Register Map7                    |  |

| Figure 1.7 Level 2-0 DMA Set Register Map 8     |  |

| Figure 1.8 DMA Force-Stop Register Map8         |  |

| Figure 1.9 DMA Status Register Map9             |  |

| Figure 1.10 DSP Program Control Port Map 9      |  |

| Figure 1.11 DSP Program RAM Data Port Map 10    |  |

| Figure 1.12 DSP Data RAM Address Port Map 10    |  |

| Figure 1.13 DSP Data RAM Data Port Map10        |  |

| Figure 1.14 Timer 0 Compare Register Map11      |  |

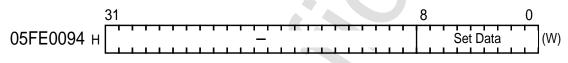

| Figure 1.15 Timer 1 Set Data Register Map11     |  |

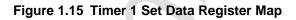

| Figure 1.16 Timer 1 Mode Register Map11         |  |

| Figure 1.17 Interrupt Mask Register Map12       |  |

| Figure 1.18 Interrupt Status Register Map12     |  |

| Figure 1.19 A-Bus Interrupt Acknowledge Map 12  |  |

| Figure 1.20 A-Bus Set Register Map13            |  |

| Figure 1.21 A-Bus Refresh Register Map13        |  |

| Figure 1.22 SCU SDRAM Select Register Map 14    |  |

| Figure 1.23 SCU Version Register Map14          |  |

# (Chapter 2 Operation)

| Figure 2.1 | DMA Transfer Basic Operation                                      | 16 |

|------------|-------------------------------------------------------------------|----|

| Figure 2.2 | DMA Transferable Area when Activacted from the Main CPU           | 17 |

| Figure 2.3 | DMA Transferable Area when Activacted from the DSP                | 17 |

| Figure 2.4 | Direct Mode DMA Transfer Operation                                | 18 |

| Figure 2.5 | Indirect Mode DMA Transfer Flow                                   | 19 |

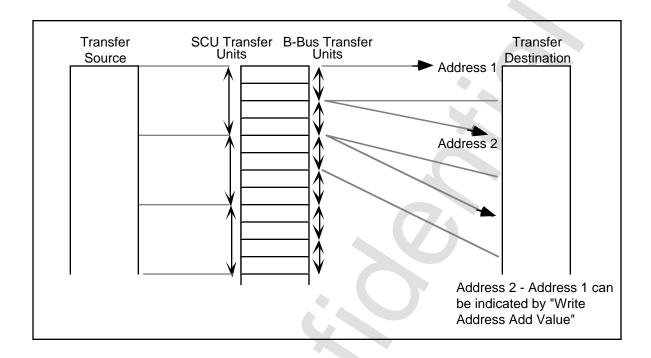

| Figure 2.6 | Indirect Mode DMA Transfer Operation Details                      | 20 |

| Figure 2.7 | Differences in DMA Operations according to the Address Update Bit | 22 |

| Figure 2.8  | Example of Data Write                                         | 23 |

|-------------|---------------------------------------------------------------|----|

| Figure 2.9  | Work RAM Area Contents                                        | 24 |

| Figure 2.10 | DMA Transfer by Setting Address Add Value                     | 26 |

| Figure 2.11 | Blanking Interrupt                                            | 29 |

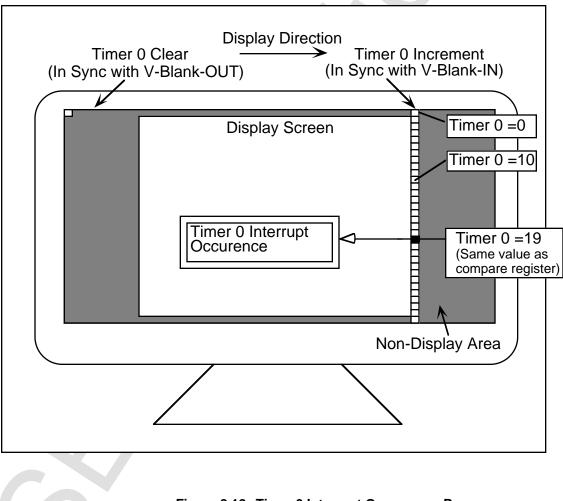

| Figure 2.12 | Timer 0 Interrupt Process (compare register = when 19 is set) | 30 |

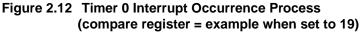

| Figure 2.13 | Timer 1 Interrupt Process (In sync with Timer 0)              | 31 |

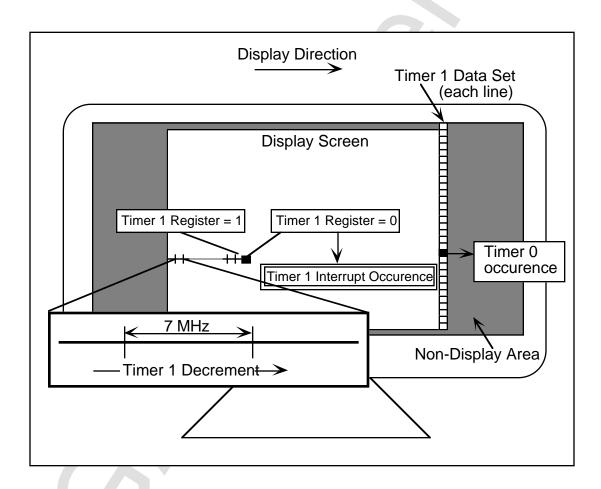

| Figure 2.14 | Timer 1 Interrupt Process (not in sync with Timer 0)          | 32 |

| Figure 2.15 | DSP Program Load Step 1                                       | 34 |

| Figure 2.16 | DSP Program Load Step 2                                       | 35 |

| Figure 2.17 | DSP Program Load Step 3                                       | 35 |

| Figure 2.18 | DSP Data Access Step 1                                        | 36 |

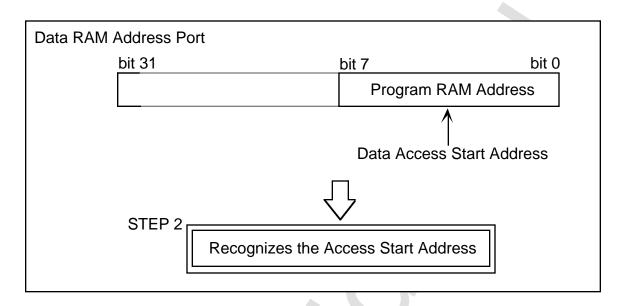

| Figure 2.19 | DSP Data Access Step 2                                        | 37 |

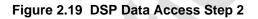

| Figure 2.20 | DSP Data Access Step 3                                        | 37 |

| Figure 2.21 | DSP Program Execution Start Control from CPU                  | 38 |

| Figure 2.22 | DSP Program Forced Stop Control from CPU                      | 38 |

## (Chapter 3 Registers)

| Figure 3.1 Level 2-0 Read Address (Register: D0R, D1R, D2R) 41             |

|----------------------------------------------------------------------------|

| Figure 3.2 Level 2-0 Write Address (Register: D0W, D1W, D2W) 41            |

| Figure 3.3 Level 0 Transfer Byte Number (Register: D0C) 42                 |

| Figure 3.4 Level 2-1 Transfer Byte Number (Register: D1C, D2C) 42          |

| Figure 3.5 Level 2-0 Address Add Value (Register: D0AD, D1AD, D2AD) 42     |

| Figure 3.6 Communication Units between the SCU and Processor               |

| Figure 3.7 Specific Example of Transfer between the SCU and Processor      |

| Figure 3.8 Write Address Add Value Indication 45                           |

| Figure 3.9 Level 2-0 DMA Authorization Bit (Register: D0EN, D1EN, D2EN) 45 |

| Figure 3.10 Level 2-0 DMA Mode, Address Update, Start Up Factor            |

| Select Register (Register: D0MP, D1MP, D2MP) 46                            |

| Figure 3.11 DMA Force-Stop Register (Register: DSTP) 47                    |

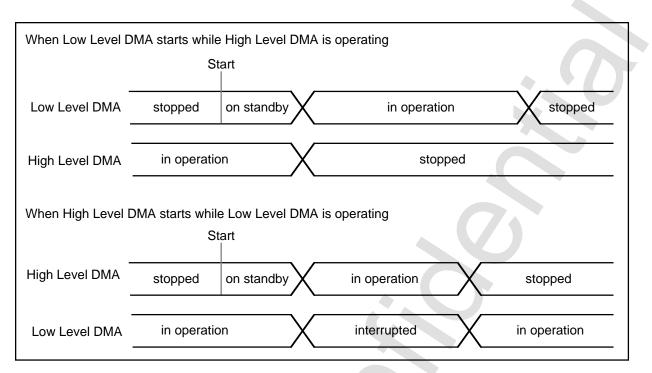

| Figure 3.12 High and Low Level DMA Operation                               |

| Figure 3.13 DMA Status Register (Register: DSTA) 48                        |

|                                                                            |

|                                                                            |

|                                                                            |

|                                                                            |

|                                                                            |

|                                                                            |

|                                                                            |

| Figure 3.14 | DSP Program Control Port (Register: PPAF)                    | 51 |

|-------------|--------------------------------------------------------------|----|

| Figure 3.15 | DSP Program RAM Data Port (Register: PPD)                    | 53 |

| Figure 3.16 | DSP Data RAM Address Port (Register: PDA)                    | 53 |

| Figure 3.17 | DSP Data RAM Data Port (Register: PDD)                       | 54 |

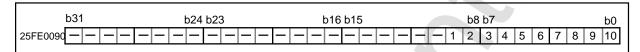

| Figure 3.18 | Time 0 Compare Register (Register: T0C)                      | 55 |

| Figure 3.19 | Timer 1 Set Data Register (Register: T1S)                    | 55 |

| Figure 3.20 | Timer 1 Mode Register (Register: T1MD)                       | 56 |

| Figure 3.21 | Interrupt Mask Register (Register: IMS)                      | 57 |

| Figure 3.22 | Interrupt Status Register (Register: IST)                    | 58 |

| Figure 3.23 | A-Bus Interrupt Acknowledge Register (Register: AIAK)        | 61 |

| Figure 3.24 | A-Bus Set [CS0, 1 Space] (Register: ASR0)                    | 62 |

| Figure 3.25 | A-Bus Set [CS2, Dummy Space] (Register: ASR1)                | 62 |

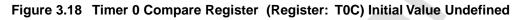

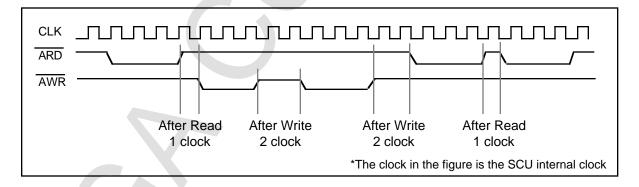

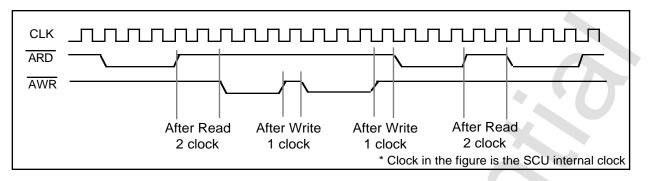

| Figure 3.26 | Result of Previous Read Process                              | 63 |

| Figure 3.27 | Timing when Setting the Pre-Charge Insert Bit after Write    | 63 |

| Figure 3.28 | Timing when Setting the Pre-Charge Insert Bit after Read     | 64 |

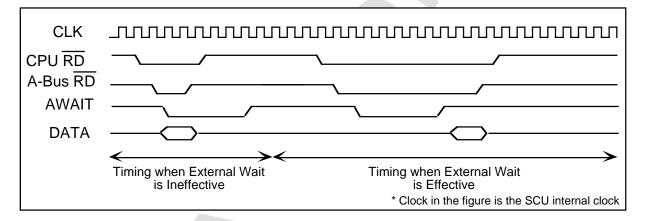

| Figure 3.29 | Differences in Timing by Setting External Wait Effective Bit | 64 |

| Figure 3.30 | A-Bus Refresh Register (Register: AREF)                      | 72 |

| Figure 3.31 | SCU SDRAM Select Bit (Register: RSEL)                        | 73 |

| Figure 3.32 | SCU Version Register (Register: VER)                         | 73 |

## Chapter 4 DSP Control)

|                                                                     | -   |

|---------------------------------------------------------------------|-----|

| pter 4 DSP Control)                                                 |     |

| Figure 4.1 DSP Internal Block Map                                   | 77  |

| Figure 4.2 Jump Command Execution                                   | 85  |

| Figure 4.3 Loop Program Execution                                   | 86  |

| Figure 4.4 Subroutine Program Execution                             | 91  |

| Figure 4.5 Operation Command Format                                 | 92  |

| Figure 4.6 Load Immediate Command Format 1 (Unconditional Transfer) | 120 |

| Figure 4.7 Load Immediate Command Format 2 (Conditional Transfer)   | 120 |

| Figure 4.8 DMA Command Format 1                                     | 132 |

| Figure 4.9 DMA Command Format 2                                     | 132 |

| Figure 4.10 Jump Command Format                                     | 141 |

| Figure 4.11 Loop Bottom Command Format                              | 153 |

| Figure 4.12 End Command Format                                      | 156 |

|                                                                     |     |

## List of Tables

#### (Chapter 2 Operation)

| Table 2.1 Interrupt Factors27                       |  |

|-----------------------------------------------------|--|

| Table 2.2 Interrupt Factor General Names         28 |  |

#### (Chapter 3 Registers)

| Table 3.1 Register List                         | . 40 |

|-------------------------------------------------|------|

| Table 3.2 Read Address Add Value                | 43   |

| Table 3.3 Write Address Add Value               | 43   |

| Table 3.4 Starting Factors                      | .46  |

| Table 3.5 RAM Page Select                       | .53  |

| Table 3.6 Timer 1 Occurrence Selection Contents | 56   |

| Table 3.7 Timer Operation Contents              | 56   |

| Table 3.8 Interrupt Status Bit Contents         | 59   |

| Table 3.9 A-Bus Interrupt Acknowledge Contents  | 61   |

| Table 3.10 CS0 Space Burst Cycle Set Values     | 65   |

| Table 3.11 CS0 Space Normal Cycle Set Values    | 65   |

| Table 3.12 CS0 Space Burst Length Set Values    | 65   |

| Table 3.13 CS0 Space Bus Size Set Values        | 66   |

| Table 3.14 CS1 Space Burst Cycle Set Values     | 67   |

| Table 3.15 CS1 Space Normal Cycle Set Values    | 67   |

| Table 3.16 CS1 Space Burst Length Set Values    | 68   |

| Table 3.17 CS1 Space Bus Size Set Values        | 68   |

| Table 3.18 CS2 Space Burst Cycle Set Values     | 69   |

| Table 3.19 CS2 Space Bus Size Set Values        | 70   |

| Table 3.20 Dummy Space Burst Cycle Set Values   | 71   |

| Table 3.21 Dummy Space Normal Cycle Set Values  | 71   |

| Table 3.22 Dummy Space Burst Length Set Values  | 71   |

| Table 3.23 Dummy Space Bus Size Set Values      | 72   |

| Table 3.24 A-Bus Refresh Wait Number            | 72   |

|                                                 |      |

|                                                 |      |

|                                                 |      |

|                                                 |      |

|                                                 |      |

|                                                 |      |

## (Chapter 4 DSP Control)

| Table 4.1 List of Commands (1)                         | . 80 |

|--------------------------------------------------------|------|

| Table 4.2 List of Commands (2)                         | . 81 |

| Table 4.3 List of Commands (3)                         | . 82 |

| Table 4.4 List of Commands (4)                         |      |

| Table 4.5 Descriptions of Constants                    | . 84 |

| Table 4.6 Features of Data Transfer from D0 Bus to DSP | 87   |

| Table 4.7 Features of Data Transfer from DSP to D0 Bus | . 88 |

## CHAPTER 1 OVERVIEW

## **Chapter 1 Contents**

| 1.1 | SCU Overview                         |    |

|-----|--------------------------------------|----|

|     | System Diagram                       | 2  |

|     | Block Diagram                        |    |

| 1.2 | SCU Mapping                          | 4  |

|     | Operation of Cache Hit               | 5  |

| 1.3 | SCU Register Map                     | 7  |

|     | Level 2-0DMA Set Register            | 8  |

|     | DMA Forced-Stop Register             | 8  |

|     | DMA Status Register                  | 9  |

|     | DSP Program Control Port             | 9  |

|     | DSP Program RAM Data Port            | 10 |

|     | DSP Data RAM Address Port            | 10 |

|     | DSP Data RAM Data Port               | 10 |

|     | Timer 0 Compare Register             | 11 |

|     | Timer 1 Set Data Register            | 11 |

|     | Timer 1 Mode Register                | 11 |

|     | Interrupt Mask Register              | 12 |

|     | Interrupt Status Register            | 12 |

|     | A-Bus Interrupt Acknowledge Register | 12 |

|     | A-Bus Set Register                   | 13 |

|     | A-Bus Refresh Register               | 13 |

|     | SCU SDRAM Select Register            | 14 |

|     | SCU Version Register                 | 14 |

|     |                                      |    |

## 1.1 SCU Overview

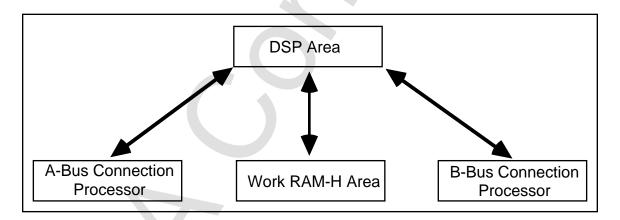

The SCU (System Control Unit) contains a CPU I/F, A-Bus I/F, and B-Bus I/F. It smoothly interfaces multiple processors connected through their respective I/Fs and buses. Also contained inside are the DMA controller, interrupt controller, and DSP.

The DMA controller controls the internal level 2-0 as well as DSP total 4 channel DMA transfer, and allows the free transfer of data between the CPU, A-Bus, and B-Bus. Using the CPU-Bus, the CPU can access the work area while executing the DMA of the A-Bus and B-Bus. The DSP region must be used in data transfer request from the DSP. For instance, DMA transfer with the A-Bus and B-Bus not using the DSP region cannot request that data be transfered from the DSP.

The interrupt controller includes interrupts from the A-Bus, B-Bus, and System Manager, and controls all interrupts within the SCU. It also supports interrupt by timers and can produce interrupts that are in sync with the screen.

DSP can handle processes that cannot be handled by the main CPU when its load has been exceeded. DSP operates at half the frequency of the main CPU. As a result, one step takes about 70 nsec.

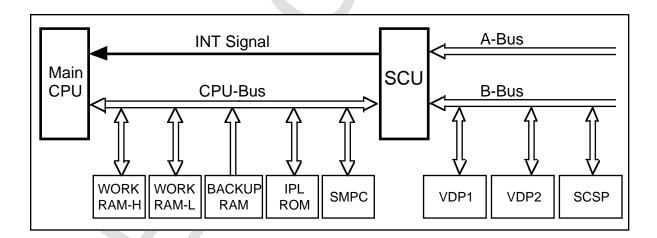

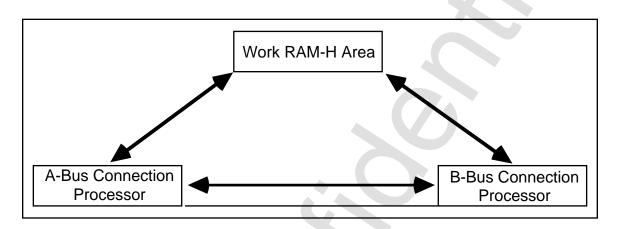

#### System Diagram

A diagram of the system is shown in Figure 1.1. The Work RAM-H, Work RAM-L, Backup RAM, IPL ROM, and SMPC are connected to the CPU-Bus. The CPU-Bus controls the system reset signal and control pad. The medium that supplies the CD or cartridge software is an external system connected to the A-Bus. VDP1, VDP2, and SCSP are connected to the B-Bus and control picture and sound.

Figure 1.1 Diagram of System

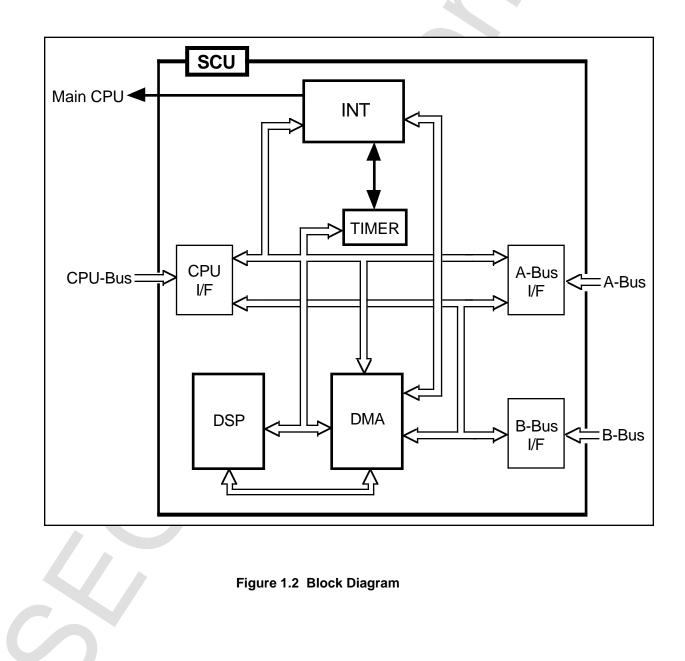

#### **Block Diagram**

A block diagram of the SCU is shown in Figure 1.2. As previously mentioned, the CPU interface, A-Bus, and B-Bus interfaces, and the DMA controller, interrupt controller, and DSP are contained in the SCU. All interfaces and controllers are connected by buses, making transfer of data possible.

The CPU I/F and A-Bus I/F connections are through two buses. The upper bus is connected through the register. The lower bus is a connection used in transferring data. Therefore, DMA transfer is done using the lower bus.

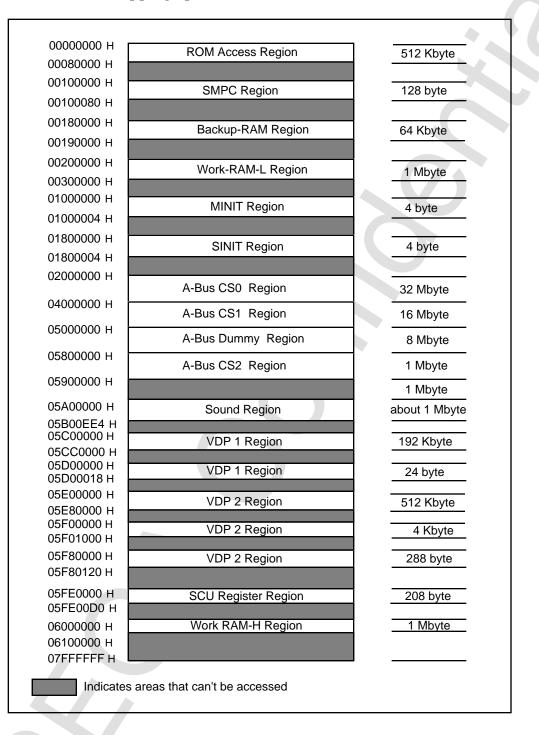

## 1.2 SCU Mapping

Figure 1.3 shows the mapping operation.

Figure 1.3 SCU Mapping (Cache\_address)

#### **Operation of Cache Hit**

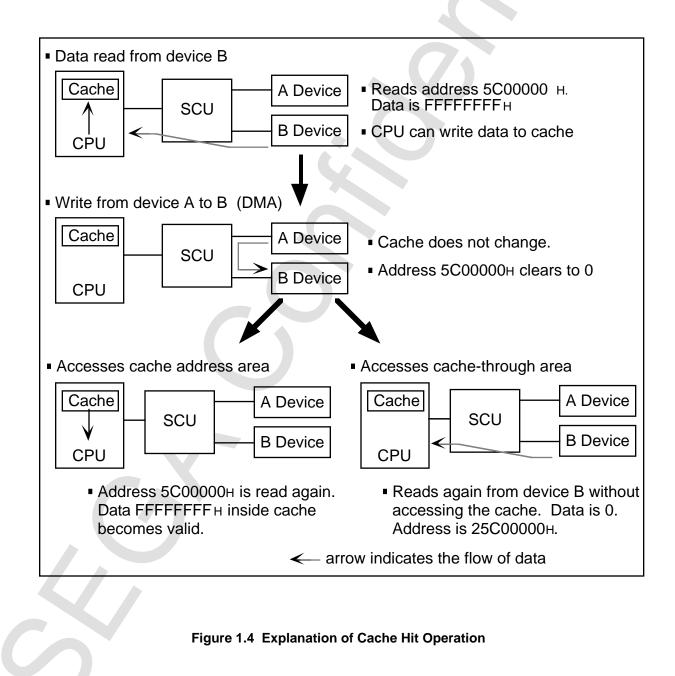

If a hit is made to the cache during access to an area that is rewritable by non-CPU devices such as the work RAM of an I/O port, an external device, or a SCU register, a value different from the actual value could be returned. When this happens, the cache-through area must be accessed.

Figure 1.4 explains cache hit operations, and Figure 1.5 shows cach-through operations.

| 20000000 н               | ROM Access Region          | 512 Kbyte     |

|--------------------------|----------------------------|---------------|

| 20080000 н               | 5                          |               |

| 20100000 н               | SMPC Region                | 128 byte      |

| 20100080 н               |                            |               |

| 20180000 н               | Backup-RAM Region          | 64 Kbyte      |

| 20190000 н               |                            |               |

| 20200000 н               | Work-RAM-L Region          | 1 Mbyte       |

| 20300000 н               |                            |               |

| 21000000 н               | MINIT Region               | 4 byte        |

| 21000004 н               |                            |               |

| 21800000 н               | SINIT Region               | 4 byte        |

| 21800004 н               |                            |               |

| 22000000 н               | A-Bus CS0                  | 32 Mbyte      |

| 24000000 н               | A-Bus CS1                  | 16 Mbyte      |

| 25000000 н               | A-Bus Dummy                | 8 Mbyte       |

| 25800000 н               | A-Bus CS2                  | 1 Mbyte       |

| 25900000 н               |                            | 1 Mbyte       |

| 25А00000 н               | Sound Region               | about 1 Mbyte |

| 25B00EE4 H<br>25C00000 н |                            | 100.1/1       |

| 25СС0000 н               | VDP 1 Region               | 192 Kbyte     |

| 25D00000 H<br>25D00018 H | VDP 1 Region               | 24 byte       |

| 25E00000 H               | VDP 2 Region               | 512 Kbyte     |

| 25E80000 H               | VDP 2 Region               | 4 Kbyte       |

| 25F01000 H<br>25F80000 H |                            |               |

| 25F80120 H               | VDP 2 Region               | 288 byte      |

| 25FE0000 H               | SCU Register Region        | 208 byte      |

| 25FE00D0 H               | Work RAM-H Region          | 1 Mbyte       |

| 26000000 H<br>26100000 H |                            | 1 Mbyte       |

| 27FFFFFFH                |                            |               |

| Indicates are            | eas that can't be accessed |               |

# Figure 1.5 SCU Mapping (Cache\_through\_address)

## 1.3 SCU Register Map

Figure 1.6 shows a map of the SCU register. The SCU register is assigned to the highest address in the SCU mapping region and, as shown in Figure 1.3, maintains a 208 byte area. Next, a map of each register region is shown.

| 25FE0000 н               | Level 0 DMA Set Register    | 32 byte |

|--------------------------|-----------------------------|---------|

| 25FE0020 н               | Level 1 DMA Set Register    | 32 byte |

| 25FE0040 н               | Level 2 DMA Set Register    | 32 byte |

| <b>25FE0060</b> н        | DMA Forced Stop             | 16 byte |

| <b>25FE0070</b> н        | DMA Status Register         | 16 byte |

| <b>25FE0080</b> н        | DSP Program Control Port    | 4 byte  |

| <b>25FE0084</b> н        | DSP Program RAM DataPort    | 4 byte  |

| <b>25FE0088</b> н        | DSP Data RAM Address Port   | 4 byte  |

| 25FE008C н               | DSP Data RAM DataPort       | 4 byte  |

| <b>25FE0090</b> н        | Timer 0 Compare Register    | 4 byte  |

| <b>25FE0094</b> н        | Timer 1 Set Data Register   | 4 byte  |

| <b>25FE0098</b> н        | Timer 1 Mode Register       | 4 byte  |

| 25FE009C н               | Free                        | 4 byte  |

| <b>25FE00A0</b> н        | Interrupt Mask Register     | 4 byte  |

| <b>25FE00A4</b> н        | Interrupt Status Register   | 4 byte  |

| <b>25FE00A8</b> н        | A-Bus Interrupt Acknowledge | 4 byte  |

| 25FE00AC н               | Free                        | 4 byte  |

| 25FE00B0 н               | A-Bus Set Register          | 8 byte  |

| 25FE00B8 н               | A-Bus Refresh Register      | 4 byte  |

| 25FE00BC н               | Free                        | 8 byte  |

| 25FE00C4 н               | SCU SDRAM Select Register   | 4 byte  |

| 25FE00C8 н               | SCU Version Register        | 4 byte  |

| 25FE00CC н<br>25FE00CF н | Free                        | 4 byte  |

Figure 1.6 SCU Register Map

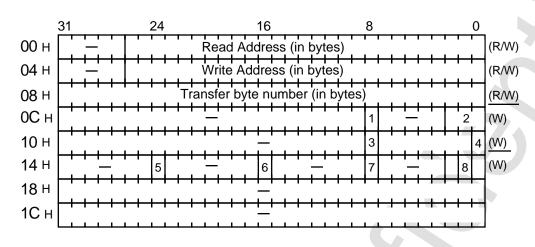

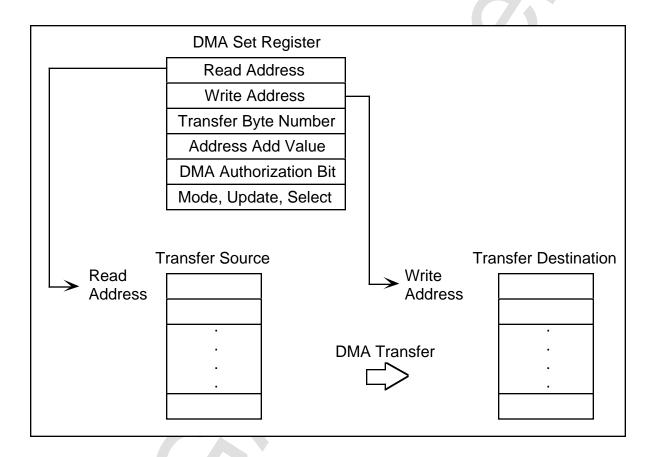

#### Level 2-0 DMA Set Register

Figure 1.7 is a map of the Level 2-0 DMA set register. Parameters required for DMA transfer are stored in this register. There are three DMA levels (from level 0 to level 2), as there are in the SCU register map (Figure 1.6). As a result, the addresses in Figure 1.7 are shown as relative addresses.

Inside graphic:

- 1. Read address add value 5. DMA mode bit (=0:Direct Mode / =1:Indirect Mode)

- 2. Write address add value 6. Read address update bit (=0:Save / =1:Revise)

- 3. DMA enable bit (=0:Disable / =1:Enable) 7. Write address update bit (=0:Save / =1:Update )

- 4. DMA starting bit

8. DMA start factor select bit

Figure 1.7 Level 2-0 DMA Set Register Map

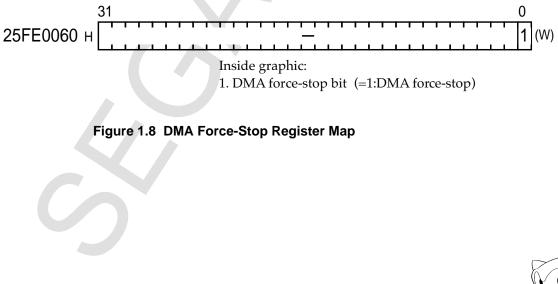

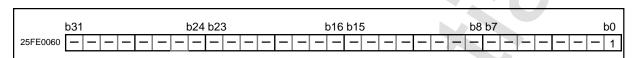

#### **DMA Force-Stop Register**

Figure 1.8 is a map of the DMA force-stop register. This register has a bit that forces the DMA operation to stop. However, if the DMA is forced to stop, it can no longer be used. This register should not be used except for debugging.

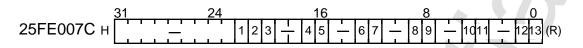

#### **DMA Status Register**

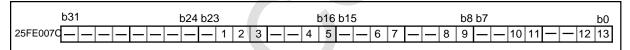

Figure 1.9 is a map of the DMA status register. This register shows level 2-0 condition status.

Inside graphic:

1. DMA DSP-Bus access flag (=0: no access /=1:access) 2. DMA B-Bus access flag (=0: no access / =1:access) 8. Level 1 DMA standby (=0:stop/=1:standby) 3. DMA A-Bus access flag (=0: no access / =1:access) 9. Level 1 DMA in operation (=0:stop/=1:operate) 4. Level 1 DMA interrupt(=0:stop/=1:interrupt) 10. Level 0 DMA stand by (=0:stop/=1:standby) 5. Level 0 DMA interrupt(=0:stop/=1:interrupt) 11. Level 0 DMA in operation (=0:stop/=1:operate) 6. Level 2 DMA standby (=0:stop/=1:standby) 12. DSP side DMA in stand by (=0:stop/=1:standby) 7. Level 2 DMA in operation (=0:stop/=1:operate)13. DSP side DMA in operation (=0:stop/=1:operate)

#### Figure 1.9 DMA Status Register Map

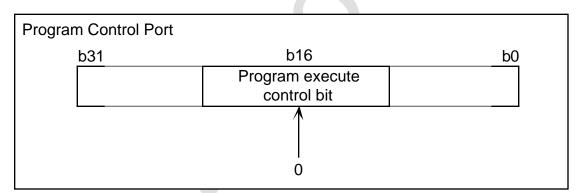

#### **DSP Program Control Port**

Figure 1.10 is a map of the DSP program control port. This is the DSP control register. It stores both the DSP operation start address and end address.

Inside graphic:

6. Carry flag

1. EX = cancels pause briefly (=0: no execute/=1:execute) 7. Overflow flag

- 2. EX = executes pause briefly (=0: no execute/=1:execute) 8. Program end interrupt flag

- 3. D0 bus use DMA transfer execution flag

- 4. Sine flag 9. Program step execute control bit (=0:no execute/=1:execute) 5. Zero flag

- 10. Program execute control (=0:stop/=1:execute)

- 11. Program counter load authorization (=0:no execute/=1:execute)

#### Figure 1.10 DSP Program Control Port Map

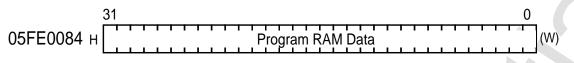

#### **DSP Program RAM Data Port**

Figure 1.11 is a map of the DSP program RAM data port. This port is used as a go-between when transferring program data from the CPU to the DSP.

Figure 1.11 DSP Program RAM Data Port Map

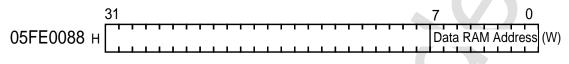

#### **DSP Data RAM Address Port**

Figure 1.12 is a map of the DSP data RAM address port. This port indicates the data RAM address while accessing the data RAM inside DSP from the CPU.

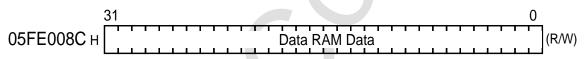

#### DSP Data RAM Data Port

Figure 1.13 is a map of the DSP data RAM data port. The content of the address shown by the DSP data RAM address port is stored. Data written from the CPU is stored in the DSP data RAM and data read from the CPU can fetch RAM data inside the DSP.

Figure 1.13 DSP Data RAM Data Port Map

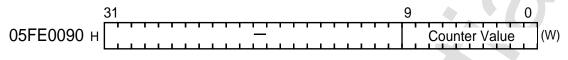

#### **Timer 0 Compare Register**

Figure 1.14 is the map of the timer 0 compare register. Timer 0 gets in sync with V-Blank-IN interrupt (See 2.2 *Interrupt Control*) and causes interrupt to occur. The operation is explained in section 2.2 and the register contents are explained in chapter 3.

#### **Timer 1 Set Data Register**

Figure 1.15 is the map timer 1 set data register. Timer 1 is *data-set* by H-Blank-IN interrupt (See 2.2 *Interrupt Control*) and decremented by 7 MHz cycles. Interrupt occurs when data is 0. The operation is explained in section 2.2 and the register contents are explained in chapter 3.

#### **Timer 1 Mode Register**

Figure 1.16 is a map of the timer 1 mode register. This register indicates the timing by which Time 1 is generated. The operation is explained in section 2.2 and the register contents are explained in chapter 3.

=1 : Timer operation ON

Figure 1.16 Timer 1 Mode Register Map

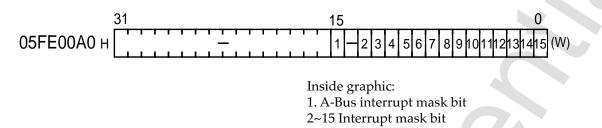

#### Interrupt Mask Register

Figure 1.17 shows the map of the interrupt mask register. When this bit is 0, interrupt is not masked and occurs as needed. When the bit is 1, interrupt will not occur because it is masked. Chapter 3 has more information about bit 0 (inside graphic, no. 15) to bit 13 (inside graphic, no. 2).

Figure 1.17 Interrupt Mask Register Map

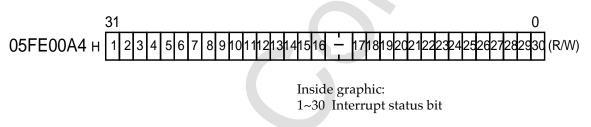

#### **Interrupt Status Register**

Figure 1.18 shows the map of the interrupt status register. Because this register is able to read and write, when reading it shows that interrupt won't occur when bit data is 0, and will occur when bit data is 1. When writing, interrupt is reset if 0 is written, and maintains the current interrupt status when 1 is written. See chapter 3 for details about this register.

Figure 1.18 Interrupt Status Register Map

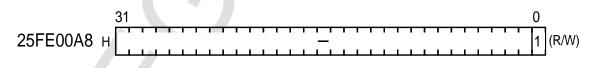

#### A-Bus Interrupt Acknowledge Register

Figure 1.19 shows a map of the A-Bus interrupt acknowledge. This is a read/write bit that has different meanings when reading vs. when writing. See chapter 3 for details.

Inside graphic:

1. READ: A-Bus interrupt acknowledge significant bit (=0:insignificant / =1:significant) WRITE: A-Bus interrupt acknowledge significant bit (=0:insignificant / =1:significant)

Figure 1.19 A-Bus Interrupt Acknowledge Register Map

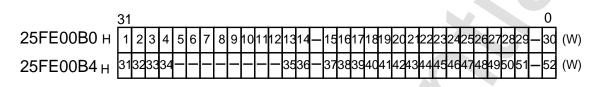

#### **A-Bus Set Register**

Figure 1.20 shows the map of the A-Bus set register. Each pre-read significant bit, precharge insertion bit, and external wait significant bit is insignificant at 0 and significant at 1. See chapter 3 for more information.

Inside graphic:

- 1. CS0 space, pre-read significant bit 31. CS2 space, pre-read significant bit 2. CS0 space, precharge insertion bit after write 32. CS2 space, precharge insertion bit after write 3. CS0 space, precharge insertion bit after read 33. CS2 space, precharge insertion bit after read 4. CS0 space, external wait significant bit 34. CS2 space, external wait significant bit 5~8. CS0 space, burst cycle wait no. set 35~36. CS2 space, burst length set bit 9~12. CS0 space, single cycle wait no. set 37. Bus size set bit (0=16 bit 1=8 bit)13~14. CS0 space, burst length set 38. Spare space, pre-read significant bit 15. CS0 space, bus size set bit (0=16bit 1=8bit) 39. Spare space, precharge insertion after write 16. CS1 space, pre-read significant bit 40. Spare space, precharge insertion after read 17. CS1 space, precharge insertion bit after write 41. Spare space, external wait significant bit 18. CS1 space, precharge insertion bit after read 42~45. Spare space, burst cycle wait no. set bit 19. CS1 space, external wait significant bit 46~49. Spare space, normal cycle wait no. set bit 20~23. CS1 space, burst cycle wait no. set 50~51. Spare space, burst length set bit 24~27. CS1 space, normal cycle wait no. set 52. Spare space, bus size set bit (0=16bit 1=8bit) 28~29. CS1 space, burst length set bit

- 30. CS1 space, bus size set bit (0=16bit 1=8bit)

#### Figure 1.20 A-Bus Set Register Map

#### **A-Bus Refresh Register**

Figure 1.21 shows the map of the A-Bus refresh register. This register performs the settings for A-Bus refresh.

Inside graphic:

A-Bus refresh output significant bit (=0:insignificant / =1:significant)

2~5. A-Bus refresh wait number set bit

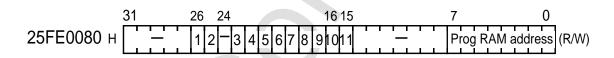

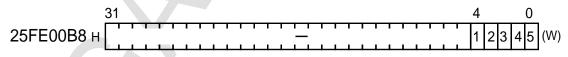

#### SCU SDRAM Select Register

Figure 1.22 shows the map of the SCU SDRAM select register.

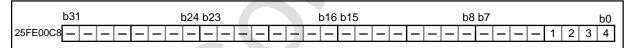

#### Figure 1.23 SCU Version Register Map

# CHAPTER 2 OPERATION

## Chapter 2 Contents

| 2.1 | DMA   | A Transfer                    | 16 |

|-----|-------|-------------------------------|----|

|     |       | Basic Operation of DMA        | 16 |

|     |       | DMA Mode                      | 18 |

|     |       | Example of A Specific Use     | 21 |

| 2.2 | Inter | rupt Control                  | 27 |

|     |       | Blanking Interrupt            | 29 |

|     |       | Timer Interrupt               | 30 |

|     |       | DSP-End Interrupt             | 33 |

|     |       | Sound-Request Interrupt       | 33 |

|     |       | SMPC Interrupt                | 33 |

|     |       | PAD Interrupt                 | 33 |

|     |       | DMA End Interrupt             | 33 |

|     |       | DMA-Illegal Interrupt         | 33 |

|     |       | Sprite Draw End Interrupt     | 33 |

| 2.3 | DSP   |                               | 34 |

|     |       | DSP Control from the Main CPU | 34 |

## 2.1 DMA Transfer

#### **Basic Operation of DMA**

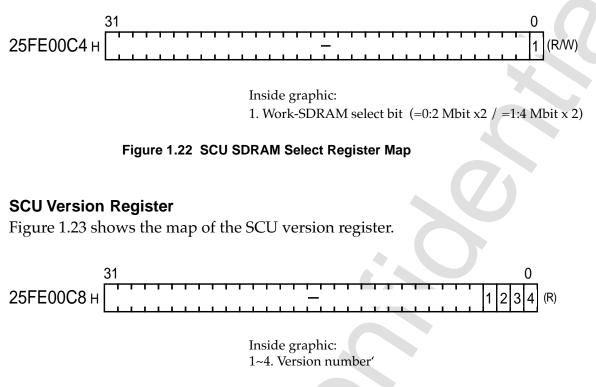

Figure 2.1 shows basic DMA operation. This DMA is basically long word access through the DMA controller buffer, but if the start address and end address are not in long word boundaries, reads and writes are made in byte units, and DMA transfer can be executed.

Figure 2.1 is an example of DMA transfer from transfer source address 1H - 50H to transfer destination address 6H - 55H. However, since the long word boundary in the transfer source is 4H, 1H - 3H is read in byte units. Since the long word boundary in the transfer destination is 8H, the first 2 bytes of read data are written to 6H - 7H in byte units. Moreover, the transfer source end address is 50H, but since the long word boundary is up to 4FH, the data in 50H is read in byte units. On the other hand, since the transfer destination end address is 55H but the long word boundary is up to 53H, the last two bytes read are written to 54H - 55H in byte units.

Figure 2.1 DMA Transfer Basic Operation

There are two methods of activating the SCU's DMA transfer control.

- 1) activate DMA from the Main CPU

- 2) activate DMA from the DSP

Figure 2.2 shows the DMA transferable area when activated from the main CPU. Figure 2.3 shows the DMA transferable area when activated from the DSP.

Figure 2.2 DMA Transferable Area when activated from the Main CPU

Figure 2.3 DMA Transferable Area when activated from the DSP

#### **DMA Mode**

The SCU DMA mode has the following two modes:

- 1) Direct Mode

- 2) Indirect Mode

#### **Direct Mode**

Data is transferred only in byte numbers shown as transfer byte numbers directly using address values of separate level DMA set registers, and from the address memory shown by the read address register to the address memory shown by the written address register. One transfer is implemented per start up, then DMA ends. Figure 2.4 shows the DMA transfer operation of the direct mode.

#### Figure 2.4 Direct Mode DMA Transfer Operation Map

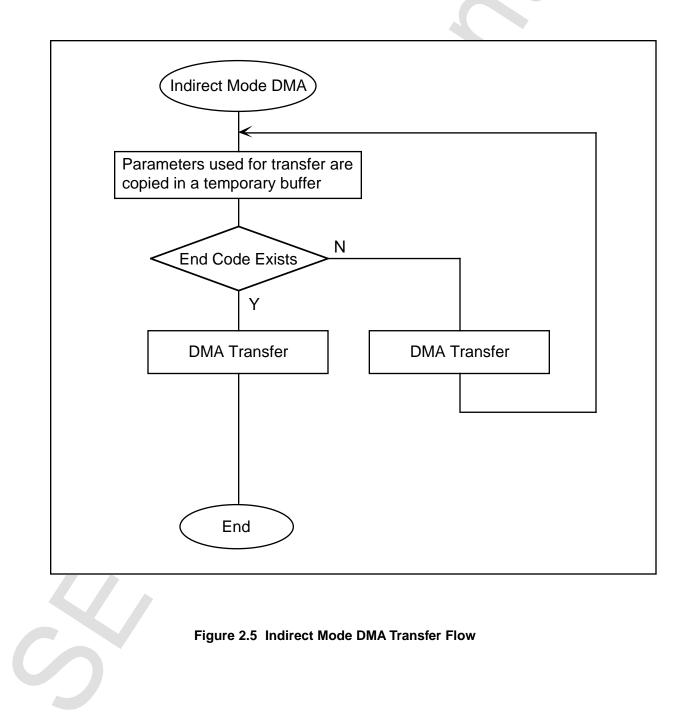

#### **Indirect Mode**

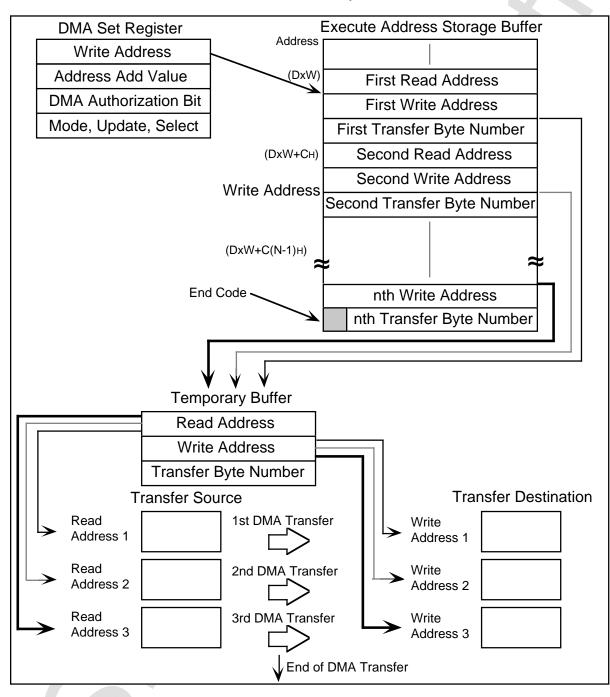

The indirect mode implements DMA transfer by indirectly using the DMA set register at a level different from the Direct mode mentioned earlier. The address value and byte number stored by the Direct mode in the set register are stored in the indirect mode temporary buffer by the Indirect mode, and DMA transfer is repeated until the end code is detected. Thus, the Indirect mode can implement more than one DMA transfer when activated once. Figure 2.5 shows the execution flow of Indirect mode DMA.

When the Indirect mode is activated, parameters of a 3 long word segment from the address first written in the write address register (DxW) is read and stored in a temporary buffer. Next, the actual DMA is executed using the parameters. On completion of DMA, the address parameters of DxW+CH are read and similarly executed. This operation is repeated until the end code is detected.

The indirect mode address is incremented in 4 byte units.

### Example of a Specific Use

### Direct Mode

A 1 Kbyte transfer can be thought of as level 0 DMA from address 2000000H (A-Bus area) to address 6000000H (work RAM). DMA (direct mode) can be executed when operating in accordance with the following procedures.

- 1) Write the read address (200000H) to the read address register D0R. (Loads the address that is read to address 25EF0000H from the CPU.)

- 2) Write the write address (6000000H) to the write address register D0W. (Loads the address that is written to address 25EF0004H from the CPU.)

- 3) Write the transfer byte number (400H) to transfer byte number register D0C. (Loads the transfer byte number from the CPU to address 25EF0008H.)

- 4) Write the address add value (101H) to address add value register D0AD. (Loads the address add value from the CPU to address 25EF000CH. Details of the address add value are listed in the address add value of this section. The address add value indicated in the normal DMA is 101H.)

- 5) The DMA mode is 0, and the address update bit and DMA start factor are set as necessary and written to mode/address/update/DMA start factor register D0MD. For example, when address update is handled as the save mode and V-Blank-IN is handled as the start factor, 0 is written to D0MD. (Loads 0 in address 25EF0014H from the CPU.)

- 6) Set 1 in the DMA enable bit. When the start factor set by step 5) occurs, DMA is activated and 1 Kbyte of data is transferred by level 0 from address 2000000H (A-Bus area) to address 6000000H (work RAM).

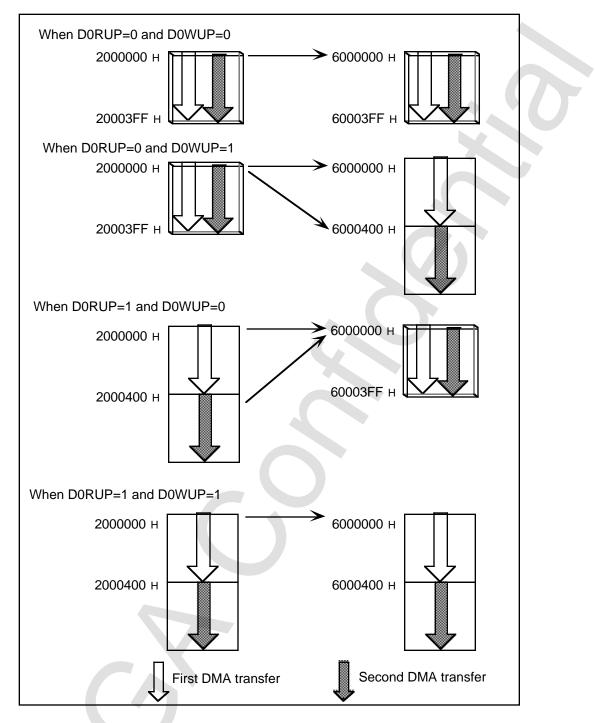

- 7) After DMA has ended, DMA is activated each time the start factor set in step 5) occurs. The operation at that time changes according to the values of the read address update bit (D0RUP) and write address update bit (D0WUP). Figure 2.7 shows DMA operation changes by the address update bit.

Steps 1) to 5) do not have to be done in the same order. (When the start factor is set in the DMA starting bit, DMA starts each time the DMA operation bit is set to 1 by the CPU.)

Figure 2.7 Differences in DMA Operations according to the Address update Bit

When the read address update bit is 0, the same address is referred to (read to) both the first and second time. When the read address update bit is 1, the second read starts after the address following the first read.

When the write address update bit is 0, write is executed to the same address for both the first and second time. When the write address update bit is 1, the second write starts after the address following the first write.

#### Indirect Mode

The Indirect mode is used when executing DMA transfer more than once by starting once. The Indirect mode is not set in a register as is the Direct mode, but uses a method of executing DMA by accessing the register through RAM. For example, consider a case in which three DMA transfers are to be continuously (consecutively) executed at level 0 through work RAM area (600000H).

- (a) 20HByte DMA transfer from 4000000H to 5C00000H

- (b) 10HByte DMA transfer from 5E00000H to 6080000H

- (c) 15HByte DMA transfer from 5A00000H to 6081000H

DMA (Indirect mode) can be executed if operated in accord with the following steps.

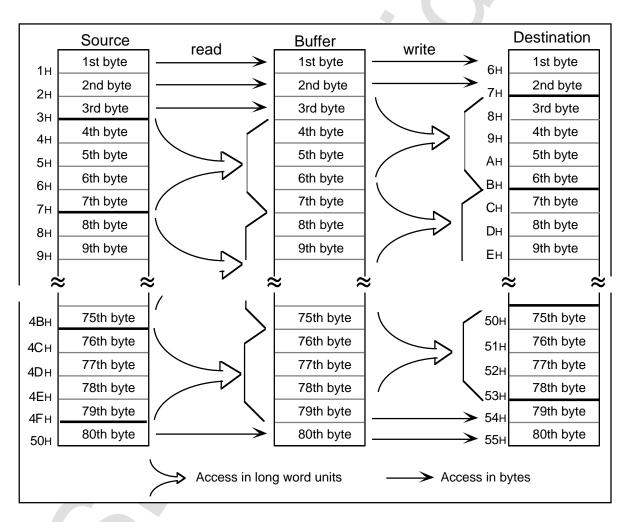

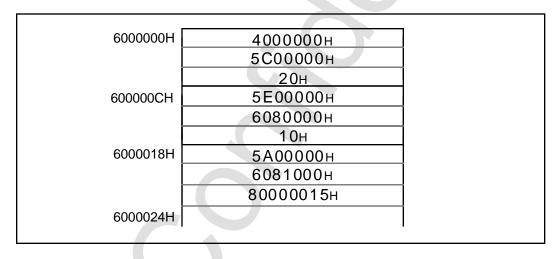

1) As shown in Figure 2.8, data is written in long word units from the work RAM area (6000000H).

Figure 2.8 Example of Data Write

- 2) DMA parameter source address (6000000H) is written to the write address register (D0W).

- 3) The address add value (101H) is loaded to the address add value register D0AD. (The address add value is written from the CPU to address 25FE000CH.) Information on the address add value is described in the address add value of this section. The address add value indicates 101H in normal DMA.

- 4) The DMA mode is 1 and the address update bit and DMA start factor are set as required and written to mode/address/update /DMA start factor register D0MP. For example, when address update is handled as the retain mode and V-Blank-IN is handled as the start factor, 1000000H is written to D0MD. (Loads 1000000H in address 25FE0014H from the CPU.)

5) "1" is set in the DMA enable bit, DMA is activated when the start factor set by step 4) occurs. DMA transfer (a) to (c) is executed in order until the DMA end code is detected. The DMA end code is the end notification code of the DMA indirect mode that exists only in the work RAM area. DMA transfer continues as long as "1" of this bit remains undetected.

Steps 1) to 4) do not need to be done in the same order. The read address register (D0R), transfer byte number register (D0C), and address add value register (D0AD), which must be set in the Direct mode, do not need to be set in the Indirect mode.

When the DMA transfers listed below are registered in memory, DMA transfer is restarted after the above process ends. Restart can be done only by repeating the operation in step (4) above.

- (d) 30HByte DMA transfer from 5000000H to 6100000H.

- (e) 25HByte DMA transfer from 5100000H to 6200000H.

The contents from the work RAM area 6000000H are shown below in Figure 2.9. DMA starts each time the start factor set by (5) occurs.

| 6000000H | <u>4000000н</u> |  |

|----------|-----------------|--|

|          | 5С0000н         |  |

|          | 20н             |  |

| 600000CH | 5Е00000н        |  |

|          | 6080000н        |  |

|          | 10н             |  |

| 6000018H | 5А00000н        |  |

|          | 6081000н        |  |

| ĺ        | 80000015н       |  |

| 6000024H | 500000н         |  |

|          | 6090000н        |  |

|          | 30н             |  |

| 6000030H | 510000н         |  |

|          | 60А0000н        |  |

|          | 80000025н       |  |

| 600003CH |                 |  |

|          |                 |  |

#### Figure 2.9 Work RAM Area Contents

The operation at restart differs depending on whether the DMA mode is in save mode or update mode. Recognition of the save/update mode of the Indirect mode is performed and judged by the write address update bit.

- For Save mode (write address update bit = 0), after one DMA transfer is completed, because the address accessing the parameters is saved at 6000000H, (a) ~ (c) DMA transfer is re-implemented.

- For update mode (write address update bit = 1), after one DMA transfer is completed, because the address accessing the parameters is updated at 6000024H, (d) ~ (e) DMA transfer is implemented.

### Address Add Value

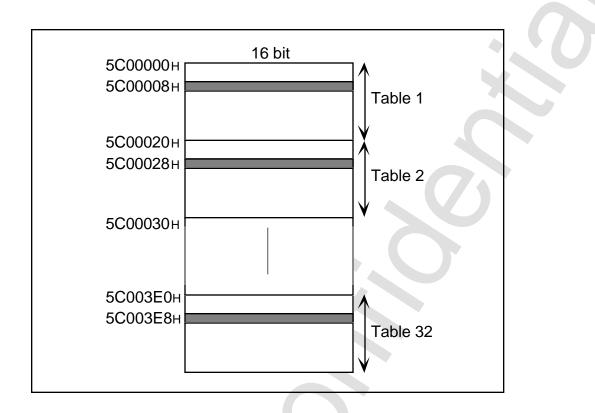

DMA normally accesses continuous areas, but by setting the address add value, the addresses of fixed intervals can be accessed. This function is effective when changing part of continuously arranged parameters like the VDP1 command table. An example is 32 blocks as one 20H byte table from address 5C00000H, among which the parameters of each 8 byte block are rewritten one time. Change parameters that have 40H bytes from address 6000000H are set by the following steps and the transfer process is implemented when transferring via level 0 of DMA.

- 1) Write the read address 6000000H to read address register D0R.

- 2) Write the write address 5C00008H to write address register D0W.

- 3) Write transfer byte number 40H to transfer byte number register D0C.

- 4) Write the address add value 105H to address add value register D0AD. Here, the low 3 bits (5=101B) updates the address for each 20H.

- 5) Set the DMA mode to 0 and set the address update bit and DMA start factor as required. Write to the mode/address /update/DMA start factor register D0MD. For example, 0 is written to D0MD when V-Blank-IN is the starting factor and address update is in a retain mode.

6) Set the DMA enable bit to 1. DMA is activated when the starting factor set in step 5) occurs and the slanted line area in Figure 2.10 is rewritten once.

Figure 2.10 DMA Transfer by Setting Address Add Value

Steps 1) through 5) do not have to be in the same order.

# 2.2 Interrupt Control

Table 2.1 shows the bit allocation of interrupt factors. Bit allocation shows the interrupt register status. Level 1 is the lowest interrupt level and level F is the highest. Details are given below for each interrupt factor.

| Bit<br>Allocation | Interrupt Factors     | Interrupt Source | Vector Number | Lev  |

|-------------------|-----------------------|------------------|---------------|------|

| bit 0             | V-Blank-IN            | VDP2             | Vector 40     | Leve |

| bit 1             | V-Blank-OUT           | VDP2             | Vector 41     | Leve |

| bit 2             | H-Blank-IN            | VDP2             | Vector 42     | Leve |

| bit 3             | Timer 0               | SCU              | Vector 43     | Leve |

| bit 4             | Timer 1               | SCU              | Vector 44     | Leve |

| bit 5             | DSP End               | SCU              | Vector 45     | Leve |

| bit 6             | Sound Request         | SCSP             | Vector 46     | Leve |

| bit 7             | System Manager        | SM               | Vector 47     | Leve |

| bit 8             | PAD Interrupt         | PAD              | Vector 48     | Leve |

| bit 9             | Level-2 DMA End       | A-Bus            | Vector 49     | Leve |

| bit 10            | Level-1 DMA End       | A-Bus            | Vector 4A     | Leve |

| bit 11            | Level-0 DMA End       | A-Bus            | Vector 4B     | Leve |

| bit 12            | DMA-illegal           | SCU              | Vector 4C     | Leve |

| bit 13            | Sprite Draw End       | VDP1             | Vector 4D     | Leve |

| bit 14            |                       |                  |               |      |

| bit 15            |                       |                  |               |      |

| bit 16            | External Interrupt 00 | A-Bus            | Vector 50     | Leve |

| bit 17            | External Interrupt 01 | A-Bus            | Vector 51     | Leve |

| bit 18            | External Interrupt 02 | A-Bus            | Vector 52     | Leve |

| bit 19            | External Interrupt 03 | A-Bus            | Vector 53     | Leve |

| bit 20            | External Interrupt 04 | A-Bus            | Vector 54     | Leve |

| bit 21            | External Interrupt 05 | A-Bus            | Vector 55     | Leve |

| bit 22            | External Interrupt 06 | A-Bus            | Vector 56     | Leve |

| bit 23            | External Interrupt 07 | A-Bus            | Vector 57     | Leve |

| bit 24            | External Interrupt 08 | A-Bus            | Vector 58     | Leve |

| bit 25            | External Interrupt 09 | A-Bus            | Vector 59     | Leve |

| bit 26            | External Interrupt 10 | A-Bus            | Vector 5A     | Leve |

| bit 27            | External Interrupt 11 | A-Bus            | Vector 5B     | Leve |

| bit 28            | External Interrupt 12 | A-Bus            | Vector 5C     | Leve |

| bit 29            | External Interrupt 13 | A-Bus            | Vector 5D     | Leve |

| bit 30            | External Interrupt 14 | A-Bus            | Vector 5E     | Leve |

| bit 31            | External Interrupt 15 | A-Bus            | Vector 5F     | Leve |

Table 2.1 Interrupt Factors

Table 2.2 shows by what general names the interrupt factors are called. Later descriptions are based on the general name.

| General Names      | Specific Names            |

|--------------------|---------------------------|

|                    | V-Blank-IN                |

| Blanking Interrupt | V-Blank-OUT               |

|                    | H-Blank-IN                |

| Timer Interrupt    | Timer 0                   |

|                    | Timer 1                   |

|                    | Level 2-DMA End Interrupt |

| DMA End Interrupt  | Level 1-DMA End Interrupt |

|                    | Level 0-DMA End Interrupt |

### **Blanking Interrupt**

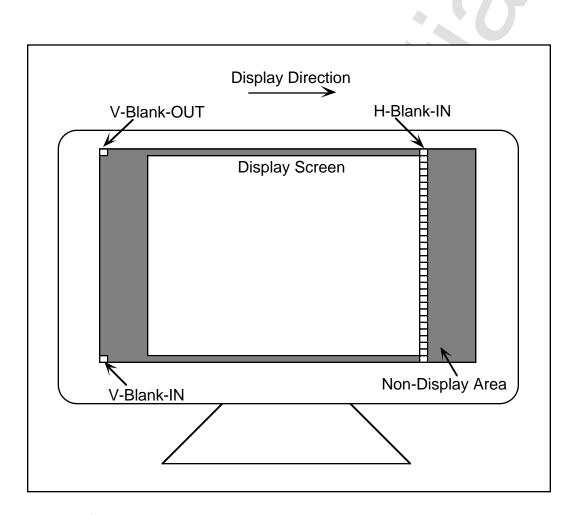

There are three types of blanking interrupt, V-Blank-IN, V-Blank-OUT, and H-Blank-IN. Figure 2.11 details blanking interrupt. Blanking interrupt is synchronous to the display, and notifies the user whether a drawing is at the beginning or end.

Figure 2.11 Blanking Interrupt

#### V-Blank-IN

Indicates the end of a display, after which nothing will be displayed on the screen even when attempting to display data.

### V-Blank-OUT

V-Blank-OUT indicates the beginning of a display. Although a display may be about to begin, how long before interrupt occurs must be taken into consideration since it takes time (an interval) for the actual display to materialize. V-Blank-OUT also clears Time 0 data.

### H-Blank-IN

H-Blank-IN indicates the draw end of one line. Timer 0 data is incremented by this timing.

### **Timer Interrupt**

Time interrupt includes Timer 0 and Timer 1. Time interrupt is synchronous with the blanking interrupt mentioned earlier and can cause interrupt to occur at dots (points) on the screen.

#### Timer 0

Values are cleared by V-Blank-OUT interrupt reception and counted by H-Blank-IN interrupt reception . Timer 0 interrupt occurs when values compared to the Timer 0 compare register (see register details) are the same. Figure 2.12 shows the Timer 0 occurrence process.

### Timer 1

Data of the Timer 1 data set register (see register details) is set by Timer 1 with H-Blank-In interrupt receiving. Count down is done at a frequency (1 dot painting) of 7 MHz or about 1/4 the system clock. When the value of Timer 1 becomes 0, interrupt of Timer 1 occurs. Interrupt can also be made to occur at 1 point by combining it with Timer 0 according to the Timer 1 mode register value (see register details), and interrupt can be caused to occur at each line independently of Timer 0. Figure 2.13 shows the process up to when Timer 1 interrupt is caused to occur in sync with Timer 0.

Figure 2.14 shows the process up to when Timer 1 is caused to occur out of sync with Timer 0. There is no change when operationally in sync but a judgment is made for each line and interrupt made to occur.

Figure 2.14 Timer 1 Interrupt Process (out of sync with Timer 0)

### **DSP-End Interrupt**

The program execution control flag (see section 3.3, *E flag of the Program Control Port*) of the program control port (see section 3.3, *Program Control Port*) is set by the DSP ENDI command (see section 4.5, *"Command" ENDI command*) and gives notice when the program has ended. By this, the main CPU can retrieve the results calculated by the DSP.

### Sound-Request Interrupt

This interrupt occurs from the SCSP. For example, to display the volume level meter on the screen when a CD (Compact Disk) is connected, interrupt from SCSP is used and reported to the main.

### SMPC Interrupt

Detailed information about interrupt that occurs from SMPC is listed in the SMPC User's Manual.

### PAD Interrupt

The occurrence of this interrupt depends on the action of the user. PAD is given as one example but other items, such as a mouse, may be connected.

### **DMA End Interrupt**

Divided by level, this interrupt notifies the user when DMA transfer has ended. There are three DMA levels from level 2 to level 0.

### DMA-Illegal Interrupt

Notifies user that DMA cannot be executed by interrupt when executing DMA that cannot be done using certain parameters.

### **Sprite Draw End Interrupt**

Notifies user via VDP1 that draw has ended.

# 2.3 DSP

### **DSP Control from the Main CPU**

This allows control of the DSP from the main CPU. DSP items that can be controlled from the CPU include:

- 1) Load DSP program

- 2) Access DSP data

- 3) Begin DSP program execution

- 4) Forced stop of DSP program

### Load DSP Program

There are two methods in which the DSP program is loaded: by using the DSP DMA command, and by writing directly to the DSP program RAM area from the main CPU. Program data can be loaded if controlled from the main CPU in the order shown below.

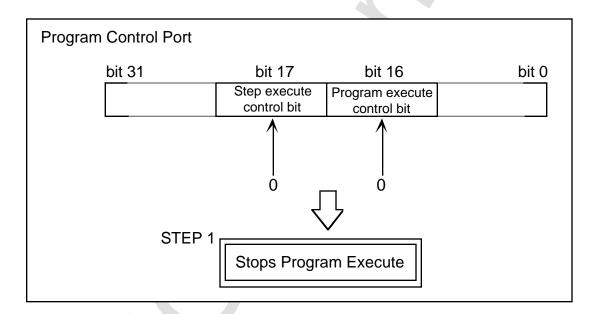

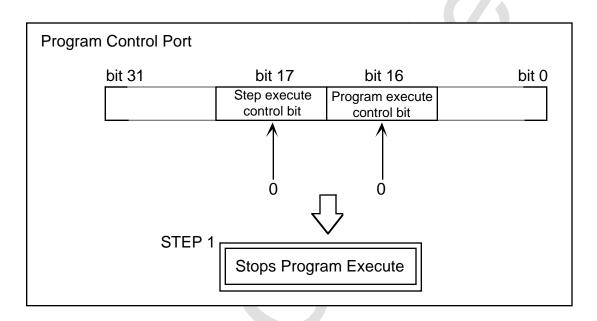

- 1) Set the program control port bits 16 and 17 to 0.

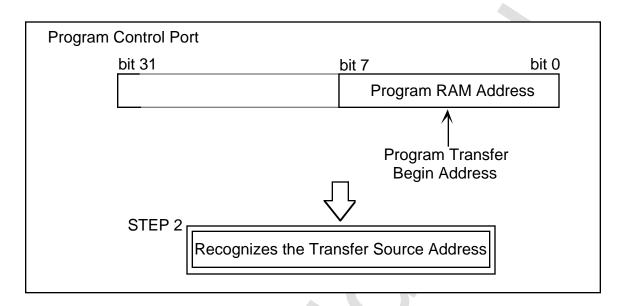

- 2) Write the transfer start address to the program RAM address of the same port. If DSP is not stopped, it cannot be loaded.

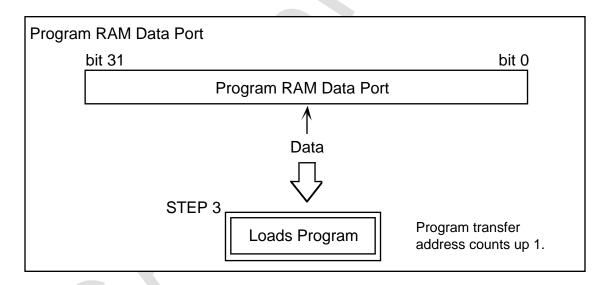

- 3) Write sequence program data in long word units to the program RAM data port.

Figures 2.15 to 2.17 show each step of control from the CPU.

Figure 2.15 DSP Program Load Step 1

Figure 2.16 DSP Program Load Step 2

Figure 2.17 DSP Program Load Step 3

#### **DSP Data Access**

In order to access DSP data, the DMA command of DSP can be used, but there is also a method that accesses the DSP data RAM area from the main CPU. Data can be accessed if controlled from the CPU in the following sequence.

- 1) Set the program control port bit 16 and bit 17 to 0.

- 2) Write the access start address to the data RAM address port. If DSP is not stopped, it cannot be set.

- 3) Sequence data is accessed in long-word units through the data RAM data port.

Control methods from the CPU for each step are shown from Figure 2.18 to Figure 2.20.

Figure 2.18 DSP Data Access Step 1

Figure 2.20 DSP Data Access Step 3

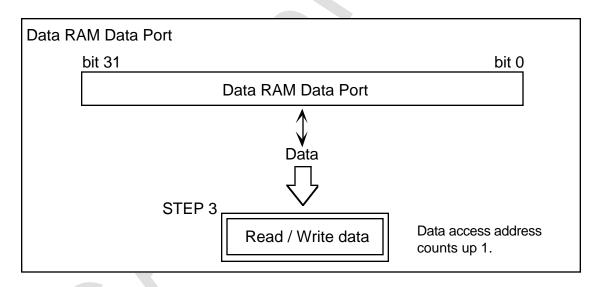

### **DSP Program Execute Start**

Execution of the DSP program is begun by writing of the program control port 1 to bit 16 (see Figure 2.21). When the write is recognized, DSP begins execution from the address stored in the program RAM address of the program control port. The execution start address must be set before writing "1" to bit 16 of the program control port.

Figure 2.21 DSP Program Execution Start Control from CPU

### **DSP Program Forced Stop**

4

In contrast to execution start, DSP program execution forced stop is done by writing the program control port 0 to bit 16 of the program control port. Figure 2.22 shows the forced stop control.

Figure 2.22 DSP Program Forced Stop Control from CPU

# CHAPTER 3 REGISTERS

# Chapter 3 Contents

| 3.1 | Register List                                          | 40 |

|-----|--------------------------------------------------------|----|

| 3.2 | DMA Control Registers                                  | 41 |

|     | Level 2-0 DMA Set Register                             | 41 |

|     | DMA Enable Register                                    | 45 |

|     | DMA Mode, Address Update, Start Factor Select Register | 46 |

|     | DMA Forced Stop Register                               | 47 |

|     | DMA Status Register                                    | 47 |

| 3.3 | DSP Control Ports                                      | 51 |

|     | DSP Program Control Port                               | 51 |

|     | DSP Program RAM Data Port                              | 53 |

|     | DSP Data RAM Address Port                              | 53 |

|     | DSP Data RAM Data Port                                 | 54 |

| 3.4 | Timer Registers                                        | 55 |

|     | Timer 0 Compare Register                               | 55 |

|     | Timer 1 Set Data Register                              | 55 |

|     | Timer 1 Mode Register                                  | 56 |

| 3.5 | Interrupt Control Registers                            | 57 |

|     | Interrupt Mask Register                                | 57 |

|     | Interrupt Status Register                              | 58 |

| 3.6 | A-Bus Control Registers                                | 61 |

|     | A-Bus Interrupt Acknowledge Register                   | 61 |

|     | A-Bus Set Register                                     | 62 |

|     | A-Bus Refresh Register                                 | 72 |

| 3.7 | SCU Control Registers                                  | 73 |

|     | SCU SDRAM Select Register                              | 73 |

|     | SCU Version Register                                   | 73 |

|     |                                                        |    |

# 3.1 Register List

A list of SCU registers is given in Table 3.1. Headings are divided for each register type and each register is explained.

| Туре                    | Register Name                | Lead Address | End Address       | Size    |

|-------------------------|------------------------------|--------------|-------------------|---------|

| DMA Control Registers   | Level 0-DMA Set Register     | 25FE0000н    | 25FE0017н         | 24 byte |

|                         | Level 1-DMA Set Register     | 25FE0020н    | <b>25FE0037</b> н | 24 byte |

|                         | Level 2-DMA Set Register     | 25FE0040н    | 25FE0057н         | 24 byte |

|                         | DMA Force-End Register       | 25FE0060н    | 25FE0063н         | 4 byte  |

|                         | DMA Status Register          | 25FE007Сн    | 25FE007Fн         | 4 byte  |

| DSP Control Ports       | DSP Program Control Port     | 25FE0080н    | 25FE0083н         | 4 byte  |

|                         | DSP Program RAM Data<br>Port | 25FE0084н    | 25FE0087н         | 4 byte  |

|                         | DSP Data RAM Address<br>Port | 25FE0088н    | 25FE008Bн         | 4 byte  |

|                         | DSP RAM Data Port            | 25FE008Сн    | 25FE008Fн         | 4 byte  |

| Timer Registers         | Timer 0 Compare Register     | 25FE0090н    | 25FE0093н         | 4 byte  |

|                         | Timer 1 Set Data Register    | 25FE0094н    | 25FE0097н         | 4 byte  |

|                         | Timer 1 Mode Register        | 25FE0098н    | 25FE009Bн         | 4 byte  |

| Interrupt Control       | Interrupt Mask Register      | 25FE00A0н    | 25FE00А3н         | 4 byte  |

| Registers               | Interrupt Status Register    | 25FE00A4н    | 25FE00A7н         | 4 byte  |

| A-Bus Control Registers | A-Bus Interrupt Acknowledge  | 25FE00А8н    | 25FE00ABн         | 4 byte  |

|                         | A-Bus Set Register           | 25FE00B0н    | 25FE00B7н         | 8 byte  |

|                         | A-Bus Refresh Register       | 25FE00B8н    | 25FE00BBн         | 4 byte  |

| SCU Control Registers   | SCU SDRAM Select Register    | 25FE00C4н    | 25FE00C7н         | 4 byte  |

|                         | SCU Version Register         | 25FE00C8н    | 25FE00CBн         | 4 byte  |

Table 3.1 Register List

# 3.2 DMA Control Registers

### Level 2-0 DMA Set Register

There are three DMA levels, beginning at the highest priority level of 2 to the lowest priority level of 0. These are explained below.

Read Address

Figure 3.1 is the read address register. The DMA mode includes a direct mode and an indirect mode. The value of the meaning changes for each mode.

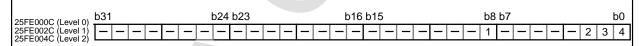

| 25FE0000 (Level 0) b31                   | b31 b24 b23 |  |      |     |   | b16 b15 |   |   |   |   |   |    |    | b8 b7 |    |    |    |    |    |    | b0 |    |    |    |    |    |    |      |    |

|------------------------------------------|-------------|--|------|-----|---|---------|---|---|---|---|---|----|----|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|------|----|

| 25FE0020 (Level 1)<br>25FE0040 (Level 2) |             |  | -  · | 1 2 | 3 | 4       | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12    | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 | 25 | 26 2 | 27 |

Figure 3.1 Level 2-0 Read Address (Register: D0R, D1R, D2R) Initail value undefined

#### **Read Address (1~27 [bit 26 ~ 0] in Figure 3.1)**

DxR 26-0[x=2-0] (R/W) DMA level 2-0 Read address bit 26-0

When in the Direct mode, values being stored are transfer source addresses. However, this has no meaning when in the Indirect mode. The register of that level prohibits writing while DMA is operating. All address values are expressed in bytes.

• Write Address

The write address register is shown in Figure 3.2. The DMA mode includes a direct mode and indirect mode; the value of the meaning changes with each mode.

| 25FE0004 (Level 0) b31                   | b24 b23     | b16 b15                 | b8 b7                     | b0          |

|------------------------------------------|-------------|-------------------------|---------------------------|-------------|

| 25FE0024 (Level 1)<br>25FE0044 (Level 2) | 1 2 3 4 5 6 | 7 8 9 10 11 12 13 14 15 | 16 17 18 19 20 21 22 23 2 | 24 25 26 27 |

Figure 3.2 Level 2-0 Write Address (Register: D0W, D1W, D2W) Initial value undefined

Write Address (1~27 [bit 26 ~ 0] in Figure 3.2)

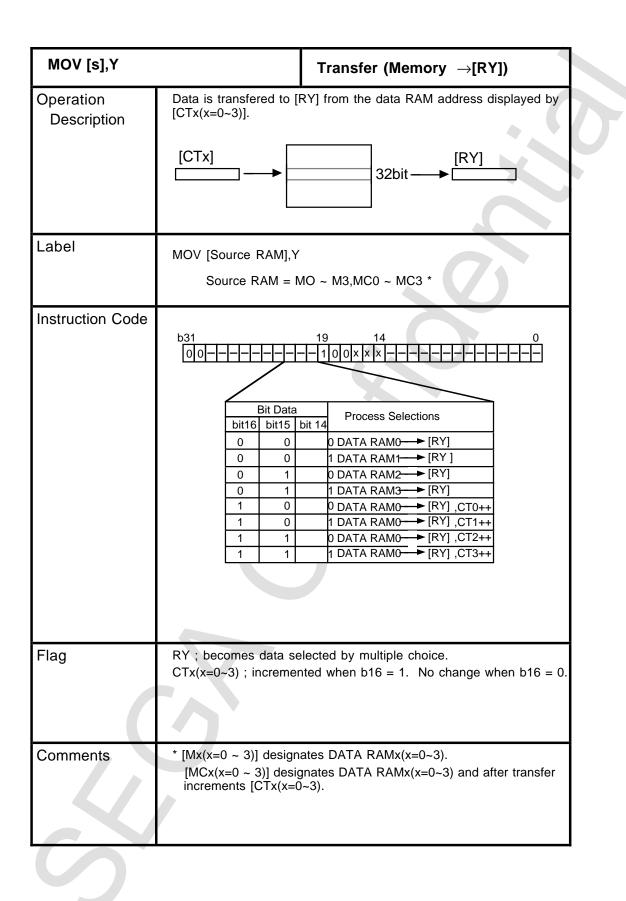

DxW 26-0[x=2-0] (R/W) DMA level 2-0 Write address bit 26-0